# PRODUCT/PROCESS CHANGE NOTIFICATION

PCN MMS-MMY/13/7707 Dated 19 Mar 2013

# M24LR04E-R, M24LR16E-R, M24LR64E-R Dual Interface EEPROM Refined design

#### Table 1. Change Implementation Schedule

| Forecasted implementation date for<br>change                                                    | 12-Mar-2013 |

|-------------------------------------------------------------------------------------------------|-------------|

| Forecasted availability date of samples for customer                                            | 12-Mar-2013 |

| Forecasted date for <b>STMicroelectronics</b><br>change Qualification Plan results availability | 12-Mar-2013 |

| Estimated date of changed product first shipment                                                | 18-Jun-2013 |

#### Table 2. Change Identification

| Product Identification<br>(Product Family/Commercial Product) | M24LR04E-R, M24LR16E-R, M24LR64E-R          |

|---------------------------------------------------------------|---------------------------------------------|

| Type of change                                                | Product design change                       |

| Reason for change                                             | Redesign refined for device limitations fix |

| Description of the change                                     | Redesign refined                            |

| Change Product Identification                                 | See marking paragraph                       |

| Manufacturing Location(s)                                     |                                             |

#### **Table 3. List of Attachments**

| Customer Part numbers list |  |

|----------------------------|--|

| Qualification Plan results |  |

|                                                           | >\$                 |

|-----------------------------------------------------------|---------------------|

| Customer Acknowledgement of Receipt                       | PCN MMS-MMY/13/7707 |

| Please sign and return to STMicroelectronics Sales Office | Dated 19 Mar 2013   |

| Qualification Plan Denied                                 | Name:               |

| Qualification Plan Approved                               | Title:              |

|                                                           | Company:            |

| 🗖 Change Denied                                           | Date:               |

| Change Approved                                           | Signature:          |

| Remark                                                    |                     |

|                                                           |                     |

|                                                           |                     |

|                                                           |                     |

|                                                           |                     |

|                                                           |                     |

|                                                           |                     |

|                                                           |                     |

| · ·····                                                   |                     |

| Name                 | Function          |

|----------------------|-------------------|

| Fidelis, Sylvain     | Marketing Manager |

| Rodrigues, Benoit    | Product Manager   |

| Malbranche, Jean-Luc | Q.A. Manager      |

### **DOCUMENT APPROVAL**

# PRODUCT / PROCESS CHANGE NOTIFICATION

### M24LR04E-R, M24LR16E-R, M24LR64E-R Dual Interface EEPROM Refined design

#### What is the change?

Following **devices limitations** described in the last revision of the corresponding **Errata sheet** (rev. 2 in APPENDIX D), the M24LR04E-R, M24LR16E-R and M24LR64E-R, 4-Kbit, 16-Kbit and 64-Kbit Dual Interface EEPROM with password protection, energy harvesting and RF status protections family products, has undergo through a refined design in order to fix:

- The RF field drop during I<sup>2</sup>C write cycle execution

- The SetRstEHEn command not functional in Addressed mode

As a consequence,

- Icc1 value has been changed from 40 µA to 100 µA at 5.5 V

- Icc1 at 1.8 V and 2.5 V being unchanged.

In addition, a T\_Prog\_flag bit has been added in the system memory to inform the application of proper execution of the write operation.

Datasheets of M24LR04E-R, M24LR16E-R and M24LR64E-R will be updated accordingly from current revisions respectively rev. 5, rev. 8, rev. 3 to new revisions respectively rev. 7, rev. 10, rev. 5.

#### Why?

The strategy of STMicroelectronics Memory Division is to support our customers on a long-term basis. In line with this commitment, the qualification of the M24LR04E-R, M24LR16E-R and M24LR64E-R with the refined design will improve service to our customers.

#### When?

The production of the M24LR04E-R, M24LR16E-R and M24LR64E-R with the design fix will ramp up from middle of March 2013 and shipments can start from end of June 2013 onward.

#### How was the change qualified?

The M24LR04E-R, M24LR16E-R and M24LR64E-R with the design fix have been qualified using the standard ST Microelectronics Corporate Procedures for Quality & Reliability.

The **Qualification Reports** QRMMY1127, QRMMY1016, QRMMY1128 are available and included inside this document.

#### What is the impact of the change?

- Form: Marking change (see **Device marking** paragraph)

- Fit: No change

- Function: Change on DC characteristics Icc1 standby supply current and addition T\_Prog\_Flag bit in system area

#### How can the change be seen?

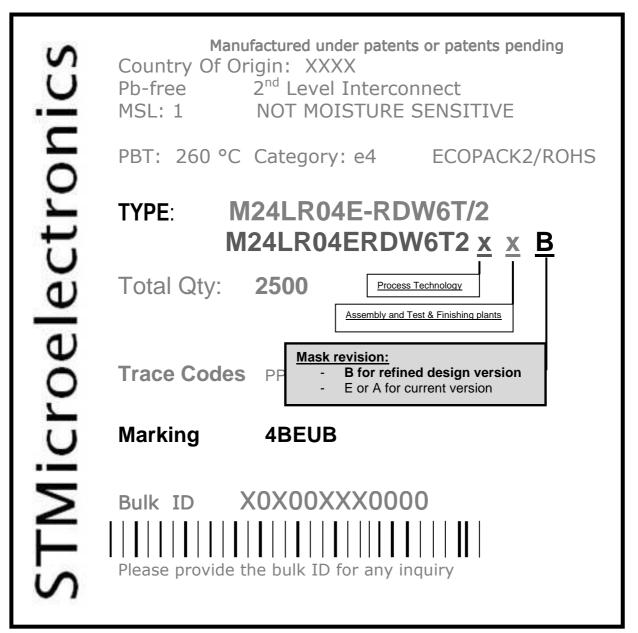

#### - BOX LABEL MARKING

On the BOX LABEL MARKING, the difference is visible inside the **Finished Good Part Number**: the **Mask revision** identifier is "**B**" for the **refined design version**, this identifier being "E" (M24LR04E-R & M24LR16E-R) or "A" (M24LR64E-R) for the current version.

→ Example for M24LR04E-RDW6T/2

#### How can the change be seen?

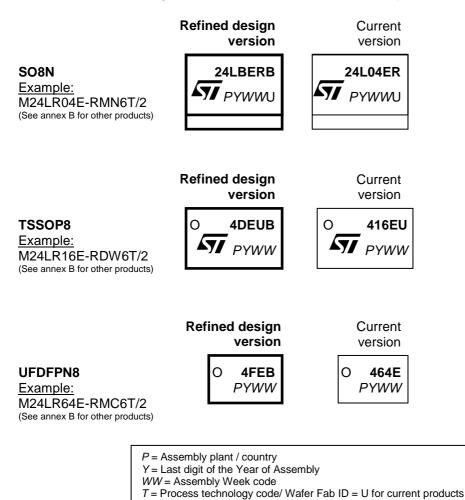

#### - DEVICE MARKING

For the device marking, the difference is visible inside the **product name** as following:

# - IC REVISION IDENTIFICATION

All involved devices have the product revision set to 0xE and below (most significant nibble of 0x911 byte).

# Appendix A- Product Change Information

| Product family / Commercial products:                                                                     | M24LR04E-R, M24LR16E-R and M24LR64E-R                                                                            |

|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

|                                                                                                           | products family                                                                                                  |

| Customer(s):                                                                                              | All                                                                                                              |

| Type of change:                                                                                           | Product design change                                                                                            |

| Reason for the change:                                                                                    | Redesign refined for device limitations fix                                                                      |

| Description of the change:                                                                                | Redesign refined                                                                                                 |

| Forecast date of the change:<br>(Notification to customer)                                                | Week 11 / 2013                                                                                                   |

| Forecast date of<br><u>Qualification samples</u> availability for<br>customer(s):                         | <ul> <li>Available for SO8N, TSSOP8 and UFDFPN8</li> <li>Bare die Week 14</li> </ul>                             |

| Forecast date for the internal<br>STMicroelectronics change,<br><u>Qualification Report</u> availability: | The Qualification Reports QRMMY1127,<br>QRMMY1016, QRMMY1128 are available and<br>included inside this document. |

| Marking to identify the changed product:                                                                  | See Device Marking paragraph                                                                                     |

| Description of the qualification program:                                                                 | Standard ST Microelectronics Corporate Procedures for Quality and Reliability                                    |

| Product Line(s) and/or Part Number(s):                                                                    | See Appendix B                                                                                                   |

| Manufacturing location:                                                                                   | Rousset 8 inch wafer fab                                                                                         |

| Estimated date of first shipment:                                                                         | Week 25 / 2013                                                                                                   |

### Appendix B: Concerned Commercial Part Numbers:

| Commercial Package<br>Part Numbers |          | Samples<br>availability | Marking (*)      |

|------------------------------------|----------|-------------------------|------------------|

| M24LR04E-RMN6T/2                   | SO8N     | Available               | 24LBERB<br>PYWWU |

| M24LR04E-RDW6T/2                   | TSSOP8   | Available               | 4BEUB<br>PYWW    |

| M24LR04E-RMC6T/2                   | UFDFPN8  | Available               | 4BEB<br>PYWW     |

| M24LR04E-RUW20/2                   | BARE DIE | Week 14                 | N/A              |

| M24LR16E-RMN6T/2                   | SO8N     | Available               | 24LDERB<br>PYWWU |

| M24LR16E-RDW6T/2                   | TSSOP8   | Available               | 4DEUB<br>PYWW    |

| M24LR16E-RMC6T/2                   | UFDFPN8  | Available               | 4DEB<br>PYWW     |

| M24LR64E-RMN6T/2                   | SO8N     | Available               | 24LFERB<br>PYWWU |

| M24LR64E-RDW6T/2                   | TSSOP8   | Available               | 4FEUB<br>PYWW    |

| M24LR64E-RMC6T/2                   | UFDFPN8  | Available               | 4FEB<br>PYWW     |

(\*) Marking available also on Datasheet and Errata sheet

# Appendix C: Qualification Report:

See following pages

# QRMMY1128 Qualification report

# New product / M24LR64E-R using the CMOSF8H technology in the Rousset 8" Fab

#### Table 1.Product information

| General information                       |                                                                                                                                                |  |  |  |  |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Commercial product                        | M24LR64E-RMN6T/2<br>M24LR64E-RDW6T/2<br>M24LR64E-RMC6T/2                                                                                       |  |  |  |  |

| Product description                       | 64-Kbit EEPROM with password protection, dual interface & energy harvesting: 400 kHz I <sup>2</sup> C bus & ISO 15693 RF protocol at 13.56 MHz |  |  |  |  |

| Product group                             | MMS                                                                                                                                            |  |  |  |  |

| Product division                          | MMY - Memory                                                                                                                                   |  |  |  |  |

| Silicon process technology                | CMOSF8H                                                                                                                                        |  |  |  |  |

| Wafer fabrication location                | RS8F - ST Rousset 8 inch, France                                                                                                               |  |  |  |  |

| Electrical Wafer Sort test plant location | ST Rousset, France<br>ST Toa Payoh, Singapore                                                                                                  |  |  |  |  |

#### Table 2. Package description

| Package description        | Qualified assembly plant location | Qualified final test plant location |

|----------------------------|-----------------------------------|-------------------------------------|

| SO8N                       | ST Shenzhen, China                | ST Shenzhen, China                  |

| TSSOP8                     | ST Shenzhen, China                | ST Shenzhen, China                  |

| UFDFPN8 (MLP8)<br>2 x 3 mm | ST Calamba, Philippines           | ST Calamba, Philippines             |

**Reliability / Qualification assessment: PASS**

# 1 Reliability evaluation overview

## 1.1 Objectives

This qualification report summarizes the results of the reliability trials that were performed to qualify the new product M24LR64E-R using the CMOSF8H silicon process technology in the ST Rousset 8" diffusion fab.

The voltage and the external RF carrier frequency covered by this document are:

- I<sup>2</sup>C interface:

- Single supply voltage: 1.8 to 5.5 V

- Contactless interface:

- ISO 15693 and ISO 18000-3 mode 1 compatible

- RF carrier frequency: 13.56 MHz ± 7 kHz

The temperature range covered by this document is:

• -40 to 85 °C

The CMOSF8H is a new advanced silicon process technology that has already been qualified in the ST Rousset 8" fab, and is in production for EEPROM products and also for dual interface EEPROM M24LR64/M24LR16E/M24LR04E products. This document serves for the qualification of the named product using the named silicon process technology in the named diffusion fab.

## 1.2 Conclusion

The new product M24LR64E-R using the CMOSF8H silicon process technology in the ST Rousset 8" diffusion fab has passed the reliability requirements and all products described in *Table 1* are qualified.

Refer to Section 3: Reliability test results for details on the reliability test results.

## 2 Device characteristics

The M24LR64E-R device is a dual-interface, electrically erasable programmable memory (EEPROM). It features an I<sup>2</sup>C interface and can be operated from a V<sub>CC</sub> power supply. It is also a contactless memory powered by the received carrier electromagnetic wave. The M24LR64E-R is organized as 8192 × 8 bits in the I<sup>2</sup>C mode and as 2048 × 32 bits in the RF mode.

The M24LR64E-R also features an energy harvesting analog output, as well as a user configurable digital output pin toggling during either RF write in progress or RF busy mode.

I<sup>2</sup>C uses a two-wire serial interface, comprising a bidirectional data line and a clock line. The devices carry a built-in 4-bit device type identifier code (1010) in accordance with the I<sup>2</sup>C bus definition.

The device behaves as a slave in the I<sup>2</sup>C protocol, with all memory operations synchronized by the serial clock. Read and Write operations are initiated by a Start condition, generated by the bus master. The Start condition is followed by a device select code and Read/Write bit (RW), terminated by an acknowledge bit.

When writing data to the memory, the device inserts an acknowledge bit during the 9<sup>th</sup> bit time, following the bus master's 8-bit transmission. When data is read by the bus master, the bus master acknowledges the receipt of the data byte in the same way. Data transfers are terminated by a Stop condition after an Ack for Write, and after a NoAck for Read.

In the ISO15693/ISO18000-3 mode 1 RF mode, the M24LR64E-R is accessed via the 13.56 MHz carrier electromagnetic wave on which incoming data is demodulated from the received signal amplitude modulation (ASK: amplitude shift keying). When connected to an antenna, the operating power is derived from the RF energy and no external power supply is required. The received ASK wave is 10% or 100% modulated with a data rate of 1.6 Kbit/s using the 1/256 pulse coding mode or a data rate of 26 Kbit/s using the 1/4 pulse coding mode.

Outgoing data is generated by the M24LR64E-R load variation using Manchester coding with one or two subcarrier frequencies at 423 kHz and 484 kHz. Data is transferred from the M24LR64E-R at 6.6 Kbit/s in low data rate mode and 26 Kbit/s high data rate mode. The M24LR64E-R supports the 53 Kbit/s fast mode in high data rate mode using one subcarrier frequency at 423 kHz.

The M24LR64E-R follows the ISO 15693 and ISO 18000-3 mode 1 recommendation for radio-frequency power and signal interface.

The M24LR64E-R provides an Energy-harvesting mode on the analog output pin Vout. When the Energy harvesting mode is activated, the M24LR64E-R can output the excess energy coming from the RF field on the Vout analog pin. In case the RF field strength is insufficient or when Energy harvesting mode is disabled, the analog output pin Vout goes into high-Z state and Energy harvesting mode is automatically stopped.

The M24LR64E-R features a user configurable digital out pin RF WIP/BUSY that can be used to drive a micro controller interrupt input pin (available only when the M24LR64E-R is correctly powered on the  $V_{CC}$  pin).

When configured in the RF write in progress mode (RF WIP mode), the RF WIP/BUSY pin is driven low for the entire duration of the RF internal write operation. When configured in the RF busy mode (RF BUSY mode), the RF WIP/BUSY pin is driven low for the entire duration of the RF command progress.

The RF WIP/BUSY pin is an open drain output and must be connected to a pull-up resistor.

Refer to the product datasheet for more details.

# 3 Reliability test results

This section contains a general description of the reliability evaluation strategy.

The named products are qualified using the standard STMicroelectronics corporate procedures for quality and reliability.

The product vehicle used for the die qualification is presented in *Table 3*.

| Product                 | Silicon process<br>technology location       |               | Package description | Assembly plant<br>location |  |

|-------------------------|----------------------------------------------|---------------|---------------------|----------------------------|--|

| M24LR64E                | CMOSF8H                                      | ST Rousset 8" | CDIP8               | Engi assy <sup>(1)</sup>   |  |

| M24LR16E <sup>(2)</sup> | 24LR16E <sup>(2)</sup> CMOSF8H ST Rousset 8" |               | CDIP8               | Engi assy <sup>(1)</sup>   |  |

Table 3.

Product vehicle used for die qualification

1. CDIP8 is a ceramic package used only for die-oriented reliability trials.

2. M24LR64E is derived from M24LR16E by metal mask option (same silicon process technology, same design core). Qualification data obtained on M24LR16E are applicable to M24LR64E.

The product vehicle used for package qualifications are presented in Table 4.

Table 4.

Product vehicle used for package qualification

| Product                                    | Silicon process<br>technology | Wafer fabrication<br>location | Package description | Assembly plant location |  |

|--------------------------------------------|-------------------------------|-------------------------------|---------------------|-------------------------|--|

| M24LR16E <sup>(1)</sup> CMOSF8H ST Rousset |                               | SO8N                          | ST Shenzhen         |                         |  |

|                                            |                               | 3001                          | Subcon Amkor P1     |                         |  |

|                                            | CMOSF8H                       | ST Rousset 8"                 | TSSOP8              | ST Shenzhen             |  |

|                                            |                               |                               | 13301.0             | Subcon Amkor P1         |  |

|                                            |                               |                               | UFDFPN8 (MLP8)      | ST Calamba              |  |

|                                            |                               |                               | 2 x 3 mm            | Subcon Amkor P3         |  |

1. M24LR64E is derived from M24LR16E by metal mask option (same silicon process technology, same design core). Qualification data obtained on M24LR16E are applicable to M24LR64E.

## 3.1 Reliability test plan and result summary

The reliability test plan and the result summary are presented as follows:

- in *Table 5* for die-oriented tests

- in Table 6 for SO8N ST Shenzhen package-oriented tests

- in Table 7 for TSSOP8 ST Shenzhen package-oriented tests

- in Table 8 for UFDFPN8 (MLP8) 2 x 3 mm ST Calamba package-oriented tests

|            | Test short description                 |                                                                                  |                  |      |                                 |                            |                     |                     |                     |                     |

|------------|----------------------------------------|----------------------------------------------------------------------------------|------------------|------|---------------------------------|----------------------------|---------------------|---------------------|---------------------|---------------------|

| Test       |                                        | Conditions                                                                       | Sample<br>size / |      | Duration                        | Results fail / sample size |                     |                     |                     |                     |

|            | Method                                 |                                                                                  |                  |      |                                 | M2                         | 4LR16E              | (2)                 | M24LR64E            |                     |

|            |                                        |                                                                                  | lots             | lots |                                 | Lot1                       | Lot2                | Lot3                | Lot4                | Lot5<br>(3)         |

|            | High temperature                       | e operating life after end                                                       | durance          |      | •<br>•                          |                            |                     |                     |                     |                     |

| EDR        | AEC-Q100-005                           | 1 million E/W cycles at<br>25 °C then:<br>HTOL 150 °C, 6 V                       | 80               | 3    | 1008 hrs                        | 0/80                       | 0/80                | 0/80                | -                   | -                   |

| EDK        | Data retention af                      | ter endurance                                                                    |                  |      |                                 |                            |                     |                     |                     |                     |

|            | AEC-Q100-005                           | 1million E/W cycles at<br>25 °C then:<br>HTSL at 150 °C                          | 80               | 3    | 1008 hrs                        | 0/80                       | 0/80                | 0/80                | -                   | -                   |

| LTOL       | Low temperature                        | operating life                                                                   |                  |      |                                 |                            | •                   |                     |                     |                     |

|            | JESD22-A108                            | –40 °C, 6 V                                                                      | 80               | 3    | 1008 hrs                        | 0/80                       | 0/80                | 0/80                | -                   | -                   |

|            | High temperature storage life          |                                                                                  |                  |      |                                 |                            |                     |                     |                     |                     |

| HTSL       | JESD22-A103                            | Retention bake at 200 °C                                                         | 80               | 3    | 1008 hrs                        | 0/80                       | 0/80                | 0/80                | -                   | -                   |

|            | Program/erase endurance cycling + bake |                                                                                  |                  |      |                                 |                            |                     |                     |                     |                     |

| WEB        | Internal spec.                         | 1 million E/W cycles at<br>25 °C then:<br>Retention bake at<br>200 °C / 48 hours | 80               | 3    | 1 million<br>cycles /<br>48 hrs | 0/80 <sup>(4)</sup>        | 0/80 <sup>(4)</sup> | 0/80 <sup>(4)</sup> | -                   | -                   |

|            | Electrostatic disc                     | charge (human body mo                                                            | odel)            |      |                                 |                            | •                   |                     |                     |                     |

| ESD<br>HBM | AEC-Q100-002                           | C = 100 pF,<br>R= 1500 Ω<br>pads AC0, AC1                                        | 27               | 3    | N/A                             | Pass<br>1000 V             | Pass<br>1000 V      | Pass<br>1500 V      | Pass<br>1000 V      | Pass<br>1000 V      |

|            | JESD22-A114                            | C = 100 pF,<br>R= 1500 Ω<br>Other pads                                           | 27               | 3    | N/A                             | Pass<br>3500 V             | Pass<br>4000 V      | Pass<br>4000 V      | Pass<br>3500 V      | Pass<br>4000 V      |

| ESD        | Electrostatic disc                     | charge (machine model)                                                           | )                |      |                                 |                            |                     |                     |                     |                     |

| ESD<br>MM  | AEC-Q100-003<br>JESD22-A115            | C = 200 pF, R = 0 Ω                                                              | 21               | 3    | N/A                             | Pass<br>400 V              | Pass<br>400 V       | Pass<br>400 V       | Pass<br>400 V       | Pass<br>400 V       |

|            | Latch-up (curren                       | t injection and overvolta                                                        | ige stress       | S)   |                                 |                            |                     |                     | -                   | -                   |

| LU         | AEC-Q100-004<br>JESD78A                | At maximum operating temperature (150 °C)                                        | 6                | 3    | N/A                             |                            | Class II<br>Level A | Class II<br>Level A | Class II<br>Level A | Class II<br>Level A |

### Table 5. Die-oriented reliability test plan and result summary (CDIP8 / Engineering package)<sup>(1)</sup>

1. See Table 9: List of terms for a definition of abbreviations.

2. M24LR64E is derived from M24LR16E by metal mask option (same silicon process technology, same design core). Qualification data obtained on M24LR16E are applicable to M24LR64E.

3. Reliability results obtained on lot 5 (refer to PCN MMS-MMY/13/7707).

4. First rejects after 5 million cycles.

|                   | Test short description      |                                                   |                  |           |                |                 |        |        |                 |  |

|-------------------|-----------------------------|---------------------------------------------------|------------------|-----------|----------------|-----------------|--------|--------|-----------------|--|

| -                 |                             |                                                   | Comula           | No.<br>of |                | Re              | e size |        |                 |  |

| Test              | Method                      | Conditions                                        | Sample<br>size / |           | Duration       | M24             | 4LR16E | (2)    | M24LR64E        |  |

|                   |                             |                                                   | lots             | lots      |                | Lot1            | Lot2   | Lot3   | Lot4            |  |

|                   | Preconditioning:            | moisture sensitivity le                           | vel 1            |           |                |                 |        |        |                 |  |

| PC                | JESD22-A113<br>J-STD-020D   | MSL1, peak<br>temperature at<br>260 °C, 3 IReflow | 345              | 3         | N/A            | 0/1145          | 0/345  | 0/1145 | -               |  |

|                   | Temperature hur             | nidity bias                                       |                  |           |                |                 |        |        |                 |  |

| THB               |                             |                                                   |                  |           | 168 hrs        | 0/80            | 0/80   | 0/80   |                 |  |

| (3)               |                             | 85 °C, 85% RH,<br>bias 5.5 V                      | 80               | 3         | 504 hrs        | 0/80            | 0/80   | 0/80   | -               |  |

|                   |                             |                                                   |                  |           | 1008 hrs       | 0/80            | 0/80   | 0/80   |                 |  |

|                   | Temperature cycling         |                                                   |                  |           |                |                 |        |        |                 |  |

| TC <sup>(3)</sup> | AEC-Q100-<br>JESD22-A104    | –65 °C / +175 °C                                  | 80               | 3         | 1000<br>cycles | 0/80            | 0/80   | 0/80   | -               |  |

| TMSK -            | Thermal shocks              |                                                   |                  |           |                |                 |        |        |                 |  |

| (3)               | JESD22-A106                 | –55 °C / +125 °C                                  | 25               | 3         | 200<br>shocks  | 0/25            | 0/25   | 0/25   | -               |  |

|                   | Autoclave (pressure pot)    |                                                   |                  |           |                |                 |        |        |                 |  |

| AC <sup>(3)</sup> | AEC-Q100-<br>JESD22-A102    | 121 °C, 100% RH at<br>2 ATM                       | 80               | 3         | 168 hrs        | 0/80            | 0/80   | 0/80   | -               |  |

|                   | High temperature            | e storage life                                    | L                |           |                |                 |        |        |                 |  |

| HTSL              |                             | Detention holes at                                |                  |           | 168 hrs        | 0/80            | 0/80   | 0/80   |                 |  |

| (3)               | AEC-Q100-<br>JESD22-A103    | Retention bake at<br>150 °C                       | 80               | 3         | 504 hrs        | 0/80            | 0/80   | 0/80   |                 |  |

|                   |                             |                                                   |                  |           | 1008 hrs       | 0/80            | 0/80   | 0/80   |                 |  |

|                   | Early failure life r        | ate                                               |                  |           |                |                 |        | -      |                 |  |

|                   | AEC-Q100-008                | HTOL 150 °C, 6V                                   | 800              | 2         | 48 hrs         | 0/800           | -      | 0/800  | -               |  |

| ESD -             |                             | charge (charge device                             | model)           |           |                |                 |        | 1      |                 |  |

| CDM               | AEC-Q100-011<br>JESD22-C101 | Field induced<br>charging method                  | 18               | 1         | N/A            | Pass<br>>1500 V | -      | -      | Pass<br>>1500 V |  |

| Table 6. | Package-oriented reliability test plan and result summary (SO8N / ST Shenzhen) <sup>(1)</sup> |

|----------|-----------------------------------------------------------------------------------------------|

1. See Table 9: List of terms for a definition of abbreviations.

2. M24LR64E is derived from M24LR16E by metal mask option (same silicon process technology, same design core). Qualification data obtained on M24LR16E are applicable to M24LR64E.

3. THB-, TC-, TMSK-, AC-, HTSL- and ELFR- dedicated parts are first subject to preconditioning flow.

|                   |                                                  |                                                   | Test sł          | nort d | escription     |                 |         |        |                 |  |  |

|-------------------|--------------------------------------------------|---------------------------------------------------|------------------|--------|----------------|-----------------|---------|--------|-----------------|--|--|

| <b>T</b> (        |                                                  |                                                   | Comula           | of     |                | Re              | e size  |        |                 |  |  |

| Test              | Method                                           | Conditions                                        | Sample<br>size / |        | Duration       | M               | 24LR16E | (2)    | M24LR64E        |  |  |

|                   |                                                  |                                                   | lots             | lots   |                | Lot1            | Lot2    | Lot3   | Lot4            |  |  |

|                   | Preconditioning:                                 | moisture sensitivity lev                          | el 1             |        |                |                 |         |        |                 |  |  |

| PC                | JESD22-A113<br>J-STD-020D                        | MSL1, peak<br>temperature at<br>260 °C, 3 IReflow | 1145             | 3      | N/A            | 0/1145          | 0/1145  | 0/1145 | -               |  |  |

|                   | Temperature hur                                  | nidity bias                                       |                  |        |                |                 |         |        |                 |  |  |

| THB               | 450.0400                                         |                                                   |                  |        | 168 hrs        | 0/80            | 0/80    | 0/80   |                 |  |  |

| (3)               | AEC-Q100- 85 °C, 85% R<br>JESD22-A101 bias 5.5 V | 85 °C, 85% RH,<br>bias 5.5 V                      | 80               | 3      | 504 hrs        | 0/80            | 0/80    | 0/80   | -               |  |  |

|                   |                                                  |                                                   |                  |        | 1008 hrs       | 0/80            | 0/80    | 0/80   |                 |  |  |

|                   | Temperature cycling                              |                                                   |                  |        |                |                 |         |        |                 |  |  |

| TC <sup>(3)</sup> | AEC-Q100-<br>JESD22-A104                         | –65 °C / +175 °C                                  | 80               | 3      | 1000<br>cycles | 0/80            | 0/80    | 0/80   | -               |  |  |

| TMSK              | Thermal shocks                                   | Thermal shocks                                    |                  |        |                |                 |         |        |                 |  |  |

| (3)               | JESD22-A106                                      | –55 °C / +125 °C                                  | 25               | 3      | 200<br>shocks  | 0/25            | 0/25    | 0/25   | -               |  |  |

|                   | Autoclave (press                                 | Autoclave (pressure pot)                          |                  |        |                |                 |         |        |                 |  |  |

| AC <sup>(3)</sup> | AEC-Q100-<br>JESD22-A102                         | 121 °C, 100% RH at<br>2 ATM                       | 80               | 3      | 168 hrs        | 0/80            | 0/80    | 0/80   | -               |  |  |

|                   | High temperature                                 | e storage life                                    |                  |        | L              |                 | L       |        | L               |  |  |

| HTSL              | 150.0400                                         | Detention halos et                                |                  |        | 168 hrs        | 0/80            | 0/80    | 0/80   |                 |  |  |

| (3)               | AEC-Q100-<br>JESD22-A103                         | Retention bake at<br>150 °C                       | 80               | 3      | 504 hrs        | 0/80            | 0/80    | 0/80   | -               |  |  |

|                   |                                                  |                                                   |                  |        | 1008 hrs       | 0/80            | 0/80    | 0/80   | 1               |  |  |

| ELFR              | Early failure life r                             | ate                                               |                  |        |                |                 |         |        |                 |  |  |

| (3)               | AEC-Q100-008                                     | HTOL 150 °C, 6V                                   | 800              | 3      | 48 hrs         | 0/800           | 0/800   | 0/800  | -               |  |  |

| ESD               | Electrostatic disc                               | charge (charge device                             | model)           | -      |                |                 |         |        |                 |  |  |

| CDM               | AEC-Q100-011<br>JESD22-C101                      | Field induced<br>charging method                  | 18               | 1      | N/A            | Pass<br>>1500 V | -       | -      | Pass<br>>1500 V |  |  |

## Table 7. Package-oriented reliability test plan and result summary (TSSOP8 / ST Shenzhen) <sup>(1)</sup>

1. See *Table 9: List of terms* for a definition of abbreviations.

M24LR64E is derived from M24LR16E by metal mask option (same silicon process technology, same design core. Qualification data obtained on M24LR16E are applicable to M24LR64E.

3. THB-, TC-, TMSK-, AC-, HTSL- and ELFR- dedicated parts are first subject to preconditioning flow.

# Table 8. Package-oriented reliability test plan and result summary (UFDFPN8 MLP8 2 x 3 mm / ST Calamba) <sup>(1)</sup>

|                   | Test short description      |                                                   |                  |           |                |                            |       |       |                 |  |

|-------------------|-----------------------------|---------------------------------------------------|------------------|-----------|----------------|----------------------------|-------|-------|-----------------|--|

|                   |                             |                                                   |                  |           |                | Results fail / sample size |       |       |                 |  |

| Test              | Method                      | Conditions                                        | Sample<br>size / | No.<br>of | Duration       | M24LR16E <sup>(2)</sup>    |       |       | M24LR64E        |  |

|                   |                             |                                                   | lots             | lots      |                | Lot1                       | Lot2  | Lot3  | Lot4            |  |

|                   | Preconditioning:            | moisture sensitivity lev                          | el 1             |           | 1              |                            |       |       |                 |  |

| PC                | JESD22-A113<br>J-STD-020D   | MSL1, peak<br>temperature at<br>260 °C, 3 IReflow | 345              | 3         | N/A            | 0/345                      | 0/345 | 0/345 | -               |  |

|                   | Temperature hur             | nidity bias                                       |                  |           |                |                            |       |       | •               |  |

| тнв               |                             |                                                   |                  |           | 168 hrs        | 0/80                       | 0/80  | 0/80  |                 |  |

| (3)               | AEC-Q100-<br>JESD22-A101    | 85 °C, 85% RH,<br>bias 5.5 V                      | 80               | 3         | 504 hrs        | 0/80                       | 0/80  | 0/80  | -               |  |

|                   |                             |                                                   |                  |           | 1008 hrs       | 0/80                       | 0/80  | 0/80  |                 |  |

|                   | Temperature cycling         |                                                   |                  |           |                |                            |       |       |                 |  |

| TC <sup>(3)</sup> | AEC-Q100-<br>JESD22-A104    | –65 °C / +175 °C                                  | 80               | 3         | 1000<br>cycles | 0/80                       | 0/80  | 0/80  | -               |  |

| TMSK              | Thermal shocks              | hermal shocks                                     |                  |           |                |                            |       |       |                 |  |

| (3)               | JESD22-A106                 | –55 °C / +125 °C                                  | 25               | 3         | 200<br>shocks  | 0/25                       | 0/25  | 0/25  | -               |  |

|                   | Autoclave (press            | ure pot)                                          |                  |           |                |                            |       |       |                 |  |

| AC <sup>(3)</sup> | AEC-Q100-<br>JESD22-A102    | 121 °C, 100% RH at<br>2 ATM                       | 80               | 3         | 168 hrs        | 0/80                       | 0/80  | 0/80  | -               |  |

|                   | High temperature            | e storage life                                    |                  |           | 1              |                            |       |       |                 |  |

| HTSL              |                             |                                                   |                  |           | 168 hrs        | 0/80                       | 0/80  | 0/80  |                 |  |

| (3)               | AEC-Q100-<br>JESD22-A103    | Retention bake at<br>150 °C                       | 80               | 3         | 504 hrs        | 0/80                       | 0/80  | 0/80  | -               |  |

|                   |                             | 100 0                                             |                  |           | 1008 hrs       | 0/80                       | 0/80  | 0/80  |                 |  |

| ESD               | Electrostatic disc          | harge (charge device i                            | model)           |           |                |                            |       |       |                 |  |

| CDM               | AEC-Q100-011<br>JESD22-C101 | Field induced charging method                     | 18               | 1         | N/A            | Pass<br>>1500 V            | -     | -     | Pass<br>>1500 V |  |

1. See *Table 9: List of terms* for a definition of abbreviations.

M24LR64E is derived from M24LR16E by metal mask option (same silicon process technology, same design core. Qualification data obtained on M24LR16E are applicable to M24LR64E.

3. THB-, TC-, TMSK-, AC-, and HTSL- dedicated parts are first subject to preconditioning flow.

## 4 Applicable and reference documents

- AEC-Q100: Stress test qualification for integrated circuits

- SOP 2.6.10: General product qualification procedure

- SOP 2.6.11: Program management fro product qualification

- SOP 2.6.12: Design criteria for product qualification

- SOP 2.6.14: Reliability requirements for product qualification

- SOP 2.6.19: Process maturity level

- SOP 2.6.2: Process qualification and transfer management

- SOP 2.6.20: New process / New product qualification

- SOP 2.6.7: Product maturity level

- SOP 2.6.9: Package and process maturity management in Back End

- SOP 2.7.5: Automotive products definition and status

- JESD22-A101: Steady state temperature humidity bias life test

- JESD22-A102: Accelerated moisture resistance unbiased autoclave

- JESD22-A103: High temperature storage life

- JESD22-A104: Temperature cycling

- JESD22-A106: Thermal shock

- JESD22-A108: Temperature, bias, and operating life

- JESD22-A113: Preconditioning of nonhermetic surface mount devices prior to reliability testing

- JESD22-A114: Electrostatic discharge (ESD) sensitivity testing human body model (HBM)

- JESD22-A115: Electrostatic discharge (ESD) sensitivity testing machine model (MM)

- JESD78A: IC Latch-up test

- J-STD-020D: Moisture/reflow sensitivity classification for nonhermetic solid state surface mount devices

# 5 Glossary

| Table 9. | List of terms |

|----------|---------------|

|----------|---------------|

| Terms   | Description                                        |  |  |  |

|---------|----------------------------------------------------|--|--|--|

| EDR     | NVM endurance, data retention and operational life |  |  |  |

| HTOL    | High temperature operating life                    |  |  |  |

| LTOL    | Low temperature operating life                     |  |  |  |

| НТВ     | High temperature bake                              |  |  |  |

| WEB     | Program/Erase endurance cycling + bake             |  |  |  |

| ESD HBM | Electrostatic discharge (human body model)         |  |  |  |

| ESD MM  | Electrostatic discharge (machine model)            |  |  |  |

| LU      | Latch-up                                           |  |  |  |

| PC      | Preconditioning (solder simulation)                |  |  |  |

| тнв     | Temperature humidity bias                          |  |  |  |

| тс      | Temperature cycling                                |  |  |  |

| тмѕк    | Thermal shocks                                     |  |  |  |

| AC      | Autoclave (pressure pot)                           |  |  |  |

| HTSL    | High temperature storage life                      |  |  |  |

| ELFR    | Early life failure rate                            |  |  |  |

| ESD CDM | Electrostatic discharge (charge device model)      |  |  |  |

# 6 Revision history

#### Table 10. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                       |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05-Apr-2012 | 1        | Initial release.                                                                                                                                                                              |

| 19-Jun-2012 | 2        | List of qualified commercial products updated in <i>Table 1</i> .<br>Added reference to UFDFPN8 (MLP8) 2 x 3 mm package in<br><i>Table 2</i> .<br><i>Table 8</i> updated with latest results. |

| 11-Feb-2013 | 3        | <i>Table 5</i> updated with reliability results obtained on lot 5 (refer to PCN MMS-MMY/13/7707).                                                                                             |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY TWO AUTHORIZED ST REPRESENTATIVES, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

# QRMMY1127 Qualification report

# New product / M24LR04E-R using the CMOSF8H technology in the Rousset 8" Fab

| General information                       |                                                                                                                                               |  |  |  |  |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Commercial product                        | M24LR04E-RMN6T/2<br>M24LR04E-RDW6T/2<br>M24LR04E-RMC6T/2                                                                                      |  |  |  |  |

| Product description                       | 4-Kbit EEPROM with password protection, dual interface & energy harvesting: 400 kHz I <sup>2</sup> C bus & ISO 15693 RF protocol at 13.56 MHz |  |  |  |  |

| Product group                             | MMS                                                                                                                                           |  |  |  |  |

| Product division                          | MMY - Memory                                                                                                                                  |  |  |  |  |

| Silicon process technology                | CMOSF8H                                                                                                                                       |  |  |  |  |

| Wafer fabrication location                | RS8F - ST Rousset 8 inch, France                                                                                                              |  |  |  |  |

| Electrical Wafer Sort test plant location | ST Rousset, France                                                                                                                            |  |  |  |  |

#### Table 1. Product information

#### Table 2.Package description

| Package description        | Qualified assembly plant location | Qualified final test plant location |  |  |  |

|----------------------------|-----------------------------------|-------------------------------------|--|--|--|

| SO8N                       | ST Shenzhen, China                | ST Shenzhen, China                  |  |  |  |

| TSSOP8                     | ST Shenzhen, China                | ST Shenzhen, China                  |  |  |  |

| UFDFPN8 (MLP8)<br>2 x 3 mm | ST Calamba, Philippines           | ST Calamba, Philippines             |  |  |  |

**Reliability / Qualification assessment: PASS**

# 1 Reliability evaluation overview

## 1.1 Objectives

This qualification report summarizes the results of the reliability trials that were performed to qualify the new product M24LR04E-R using the CMOSF8H silicon process technology in the ST Rousset 8" diffusion fab.

The voltage and the external RF carrier frequency covered by this document are:

- I<sup>2</sup>C interface:

- Single supply voltage: 1.8 to 5.5 V

- Contactless interface:

- ISO 15693 and ISO 18000-3 mode 1 compatible

- RF carrier frequency: 13.56 MHz ± 7 kHz

The temperature range covered by this document is:

• -40 to 85 °C

The CMOSF8H is a new advanced silicon process technology that has already been qualified in the ST Rousset 8" fab, and is in production for EEPROM products and also for dual interface EEPROM M24LR64/M24LR16E products. This document serves for the qualification of the named product using the named silicon process technology in the named diffusion fab.

## 1.2 Conclusion

The new product M24LR04E-R using the CMOSF8H silicon process technology in the ST Rousset 8" diffusion fab has passed the reliability requirements and all products described in *Table 1* are qualified.

Refer to Section 3: Reliability test results for details on the reliability test results.

## 2 Device characteristics

The M24LR04E-R device is a dual-interface, electrically erasable programmable memory (EEPROM). It features an I<sup>2</sup>C interface and can be operated from a V<sub>CC</sub> power supply. It is also a contactless memory powered by the received carrier electromagnetic wave. The M24LR04E-R is organized as 512 × 8 bits in the I<sup>2</sup>C mode and as 128 × 32 bits in RF mode.

The M24LR04E-R also features an energy harvesting analog output, as well as a user configurable digital output pin toggling during either RF write in progress or RF busy mode.

I<sup>2</sup>C uses a two-wire serial interface, comprising a bidirectional data line and a clock line. The devices carry a built-in 4-bit device type identifier code (1010) in accordance with the I<sup>2</sup>C bus definition.

The device behaves as a slave in the I<sup>2</sup>C protocol, with all memory operations synchronized by the serial clock. Read and Write operations are initiated by a Start condition, generated by the bus master. The Start condition is followed by a device select code and Read/Write bit (RW), terminated by an acknowledge bit.

When writing data to the memory, the device inserts an acknowledge bit during the 9<sup>th</sup> bit time, following the bus master's 8-bit transmission. When data is read by the bus master, the bus master acknowledges the receipt of the data byte in the same way. Data transfers are terminated by a Stop condition after an Ack for Write, and after a NoAck for Read.

In the ISO15693/ISO18000-3 mode 1 RF mode, the M24LR04E-R is accessed via the 13.56 MHz carrier electromagnetic wave on which incoming data are demodulated from the received signal amplitude modulation (ASK: amplitude shift keying). When connected to an antenna, the operating power is derived from the RF energy and no external power supply is required. The received ASK wave is 10% or 100% modulated with a data rate of 1.6 Kbit/s using the 1/256 pulse coding mode or a data rate of 26 Kbit/s using the 1/4 pulse coding mode.

Outgoing data are generated by the M24LR04E-R load variation using Manchester coding with one or two subcarrier frequencies at 423 kHz and 484 kHz. Data are transferred from the M24LR04E-R at 6.6 Kbit/s in low data rate mode and 26 Kbit/s high data rate mode. The M24LR04E-R supports the 53 Kbit/s fast mode in high data rate mode using one subcarrier frequency at 423 kHz.

The M24LR04E-R follows the ISO 15693 and ISO 18000-3 mode 1 recommendation for radio-frequency power and signal interface.

The M24LR04E-R provides an Energy-harvesting mode on the analog output pin Vout. When the Energy harvesting mode is activated, the M24LR04E-R can output the excess energy coming from the RF field on the Vout analog pin. In case the RF field strength is insufficient or when Energy harvesting mode is disabled, the analog output pin Vout goes into high-Z state and Energy harvesting mode is automatically stopped.

The M24LR04E-R features a user configurable digital out pin RF WIP/BUSY that can be used to drive a micro controller interrupt input pin (available only when the M24LR04E-R is correctly powered on the  $V_{cc}$  pin).

When configured in the RF write in progress mode (RF WIP mode), the RF WIP/BUSY pin is driven low for the entire duration of the RF internal write operation. When configured in the RF busy mode (RF BUSY mode), the RF WIP/BUSY pin is driven low for the entire duration of the RF command progress.

The RF WIP/BUSY pin is an open drain output and must be connected to a pull-up resistor.

Refer to the product datasheet for more details.

57

# 3 Reliability test results

This section contains a general description of the reliability evaluation strategy.

The named products are qualified using the standard STMicroelectronics corporate procedures for quality and reliability.

The product vehicle used for the die qualification is presented in *Table 3*.

| Product                 | Product Silicon process technology |               | Package description | Assembly plant location  |  |

|-------------------------|------------------------------------|---------------|---------------------|--------------------------|--|

| M24LR04E                | CMOSF8H                            | ST Rousset 8" | CDIP8               | Engi assy <sup>(1)</sup> |  |

| M24LR16E <sup>(2)</sup> | CMOSF8H                            | ST Rousset 8" | CDIP8               | Engi assy <sup>(1)</sup> |  |

Table 3.

Product vehicle used for die qualification

1. CDIP8 is a ceramic package used only for die-oriented reliability trials.

2. M24LR04E is derived from M24LR16E by metal mask option (same silicon process technology, same design core. Qualification data obtained on M24LR16E are applicable.

The product vehicle used for package qualifications are presented in Table 4.

Table 4.

Product vehicle used for package qualification

| Product                 | Silicon process<br>technology | Wafer fabrication<br>location | Package description | Assembly plant location |

|-------------------------|-------------------------------|-------------------------------|---------------------|-------------------------|

|                         |                               |                               | SO8N                | ST Shenzhen             |

|                         | CMOSF8H                       |                               | 3001                | Subcon Amkor P1         |

| M24LR16E <sup>(1)</sup> |                               | ST Rousset 8"                 | TSSOP8              | ST Shenzhen             |

|                         |                               | STROUSSELO                    | 1330F0              | Subcon Amkor P1         |

|                         |                               |                               | UFDFPN8 (MLP8)      | ST Calamba              |

|                         |                               |                               | 2 x 3 mm            | Subcon Amkor P3         |

M24LR04E is derived from M24LR16E by metal mask option (same silicon process technology, same design core. Qualification data obtained on M24LR16E are applicable.

## 3.1 Reliability test plan and result summary

The reliability test plan and the result summary are presented as follows:

- in *Table 5* for die-oriented tests

- in *Table 6* for SO8N ST Shenzhen package-oriented tests

- in Table 7 for TSSOP8 ST Shenzhen package-oriented tests

- in Table 8 for UFDFPN8 (MLP8) 2 x 3 mm ST Calamba package-oriented tests

|            | 5. Die-oriented reliability test plan and result summary (CDIP8 / Engineering package)(*/ |                                                                                  |                  |           |                                 |                     |                            |                     |                     |                     |  |

|------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------|-----------|---------------------------------|---------------------|----------------------------|---------------------|---------------------|---------------------|--|

|            |                                                                                           |                                                                                  |                  |           |                                 |                     | Results fail / sample size |                     |                     |                     |  |

| Test       | Method                                                                                    | Conditions                                                                       | Sample<br>size / | No.<br>of | Duration                        | M                   | 24LR16E                    | (2)                 | M24LR04E            |                     |  |

|            |                                                                                           |                                                                                  | lots             | lots      |                                 | Lot 1               | Lot 2                      | Lot 3               | Lot 4               | Lot 5<br>(3)        |  |

|            | High temperature                                                                          | e operating life after end                                                       | urance           |           |                                 |                     |                            |                     |                     | -                   |  |

|            | AEC-Q100-005                                                                              | 1 million E/W cycles at<br>25 °C then:<br>HTOL 150 °C, 6 V                       | 80               | 3         | 1008 hrs                        | 0/80                | 0/80                       | 0/80                | -                   | -                   |  |

| EDR        | Data retention af                                                                         | ter endurance                                                                    |                  |           |                                 | •                   |                            |                     |                     | •                   |  |

|            | AEC-Q100-005                                                                              | 1million E/W cycles at<br>25 °C then:<br>HTSL at 150 °C                          | 80               | 3         | 1008 hrs                        | 0/80                | 0/80                       | 0/80                | -                   | -                   |  |

| LTOL       | Low temperature operating life                                                            |                                                                                  |                  |           |                                 |                     |                            |                     |                     |                     |  |

| LIUL       | JESD22-A108                                                                               | –40 °C, 6 V                                                                      | 80               | 3         | 1008 hrs                        | 0/80                | 0/80                       | 0/80                | -                   | -                   |  |

|            | High temperature storage life                                                             |                                                                                  |                  |           |                                 |                     |                            |                     |                     |                     |  |

| HTSL       | JESD22-A103                                                                               | Retention bake at 200<br>°C                                                      | 80               | 3         | 1008 hrs                        | 0/80                | 0/80                       | 0/80                | -                   | -                   |  |

|            | Program/erase e                                                                           | endurance cycling + bake                                                         | Э                |           |                                 | •                   |                            |                     |                     | •                   |  |

| WEB        | Internal spec.                                                                            | 1 million E/W cycles at<br>25 °C then:<br>Retention bake at<br>200 °C / 48 hours | 80               | 3         | 1 million<br>cycles /<br>48 hrs | 0/80 <sup>(4)</sup> | 0/80 <sup>(4)</sup>        | 0/80 <sup>(4)</sup> | -                   | -                   |  |

|            | Electrostatic disc                                                                        | harge (human body mo                                                             | del)             |           |                                 |                     |                            |                     |                     |                     |  |

| ESD<br>HBM | AEC-Q100-002                                                                              | C = 100 pF, R= 1500 Ω<br>pads AC0, AC1                                           | 27               | 2         | N/A                             | Pass<br>1000 V      | Pass<br>1000 V             | Pass<br>1500 V      | Pass<br>1000 V      | Pass<br>1000 V      |  |

|            | JESD22-A114                                                                               | C = 100 pF, R= 1500 Ω<br>Other pads                                              | 21               | 3         | N/A                             | Pass<br>3500 V      | Pass<br>4000 V             | Pass<br>4000 V      | Pass<br>4000 V      | Pass<br>3500 V      |  |

| ESD        | Electrostatic disc                                                                        | charge (machine model)                                                           |                  |           |                                 | •                   |                            |                     |                     | •                   |  |

| MM         | AEC-Q100-003<br>JESD22-A115                                                               | C = 200 pF, R = 0 Ω                                                              | 21               | 3         | N/A                             | Pass<br>400 V       | Pass<br>400 V              | Pass<br>400 V       | Pass<br>400 V       | Pass<br>400 V       |  |

|            | Latch-up (curren                                                                          | t injection and overvolta                                                        | ge stress        | ;)        |                                 |                     |                            |                     |                     |                     |  |

| LU         | AEC-Q100-004<br>JESD78A                                                                   | At maximum operating temperature (150 °C)                                        | 6                | 3         | N/A                             | Class II<br>Level A | Class II<br>Level A        | Class II<br>Level A | Class II<br>Level A | Class II<br>Level A |  |

| Table 5. | Die-oriented reliability test plan and result summary (CDIP8 / Engineering package) <sup>(1)</sup> |

|----------|----------------------------------------------------------------------------------------------------|

1. See *Table 9: List of terms* for a definition of abbreviations.

2. M24LR04E is derived from M24LR16E by metal mask option (same silicon process technology, same design core. Qualification data obtained on M24LR16E are applicable.

3. Reliability results obtained on lot 5 (refer to PCN MMS-MMY/13/7707).

4. First rejects after 5 million cycles.

57

|                   | Test short description                        |                                                   |                  |           |                |                            |       |            |                 |  |

|-------------------|-----------------------------------------------|---------------------------------------------------|------------------|-----------|----------------|----------------------------|-------|------------|-----------------|--|

| Test              | Method                                        | Conditions                                        | Sample<br>size / | No.<br>of | Duration       | Results fail / sample size |       |            |                 |  |

|                   |                                               |                                                   |                  |           |                | M24LR16E <sup>(2)</sup>    |       |            | M24LR04E        |  |

|                   |                                               |                                                   | lots             | lots      |                | Lot1                       | Lot2  | Lot3       | Lot4            |  |

|                   | Preconditioning                               | g: moisture sensitivity leve                      | el 1             |           |                |                            |       |            |                 |  |

| PC                | JESD22-<br>A113<br>J-STD-020D                 | MSL1, peak<br>temperature at 260 °C,<br>3 IReflow | 345              | 3         | N/A            | 0/1145                     | 0/345 | 0/114<br>5 | -               |  |

|                   | Temperature h                                 | umidity bias                                      |                  |           |                |                            |       |            |                 |  |

| THB               | AEC-Q100-                                     | 85 °C, 85% RH,                                    |                  |           | 168 hrs        | 0/80                       | 0/80  | 0/80       |                 |  |

| (3)               | JESD22-                                       | bias 5.5 V                                        | 80               | 3         | 504 hrs        | 0/80                       | 0/80  | 0/80       | -               |  |

|                   | A101                                          |                                                   |                  |           | 1008 hrs       | 0/80                       | 0/80  | 0/80       |                 |  |

|                   | Temperature cy                                | /cling                                            | -                |           |                |                            |       |            |                 |  |

| TC <sup>(3)</sup> | AEC-Q100-<br>JESD22-<br>A104                  | –65 °C / +175 °C                                  | 80               | 3         | 1000<br>cycles | 0/80                       | 0/80  | 0/80       | -               |  |

| TMSK              | Thermal shock                                 | S                                                 |                  |           |                |                            |       |            |                 |  |

| (3)               | JESD22-<br>A106                               | –55 °C / +125 °C                                  | 25               | 3         | 200<br>shocks  | 0/25                       | 0/25  | 0/25       | -               |  |

|                   | Autoclave (pressure pot)                      |                                                   |                  |           |                |                            |       |            |                 |  |

| AC <sup>(3)</sup> | AEC-Q100-<br>JESD22-<br>A102                  | 121 °C, 100% RH at<br>2 ATM                       | 80               | 3         | 168 hrs        | 0/80                       | 0/80  | 0/80       | -               |  |

|                   | High temperatu                                | ire storage life                                  |                  |           |                |                            |       | J          |                 |  |

| HTSL <sup>(</sup> | AEC-Q100-                                     |                                                   |                  |           | 168 hrs        | 0/80                       | 0/80  | 0/80       |                 |  |